# **Ludwig-Maximilians-University Munich**

## **Faculty of Physics**

Submitted by: Dr. Eduard Prinker

Referee: Prof. Dr. Christian Kiesling

Munich, August 2015

Abstract 2

#### **Abstract**

DEPFET pixel sensors offer intrinsic amplification, low mass and a very high signal to noise ratio. They form an integral building block for the vertex detector system of the Belle II experiment, which will start data taking in the year 2017 at the new Super-KEKB electron-positron collider in Japan. The particle bunch currents have a rather short lifetime in the order of 10 minutes. To keep the significantly increased luminosity of the collider constant over time, the bunch currents have to be topped off by injecting daughter bunches at a rate of 50 Hz. The particles in the daughter bunches produce a high rate of background ("noisy bunches") for a short period of time, saturating the occupancy of the sensor. Operating the DEPFET sensor in a so far unexplored new mode ("Gated Mode") allows preserving the signals from collisions of normal bunches while protecting the pixels from background signals of the passing noisy bunches. A special test board (Hybrid 4.1) is used, which contains a small version of the DEPFET sensor with a read-out (DCDB) and a steering chip (SwitcherB) attached, both controlled by a field-programmable gate array (FPGA) as the central interface to the computer. Experimental results presented in this thesis demonstrate that the Gated Mode can be efficiently operated at full target operation speed of 320 MHz.

## Zusammenfassung

DEPFET Pixelsensoren zeichnen sich insbesondere durch ihre geringe Masse und ein hohes Signal/Rausch-Verhältnis aus. Sie bilden einen integralen Bestandteil des Belle II Vertex-Detektor-Systems am SuperKEKB Elektron-Positron-Beschleuniger in Japan, dessen Fertigstellung für 2017 geplant ist. Um die vorhandene, stark gestiegene Luminosität des Beschleunigers aufrechtzuerhalten, müssen die Teilchenpakete, deren durchschnittliche Lebensdauer ungefähr 10 Minuten beträgt, regelmäßig erneuert werden. Konkret werden alle 20 Millisekunden zwei zusätzliche Teilchenpakete in den Beschleuniger eingespeist. Die neu injizierten Teilchen verursachen zwischenzeitlich ein hohes Hintergrundrauschen. Dadurch stellen sich die Detektoraufzeichnungen als stark verzerrt und somit unbrauchbar dar. Eine spezielle Betriebsweise des DEPFET Sensors, der sogenannte "Gated Mode" ermöglicht es, dass bereits aufgezeichnete Signale erhalten bleiben und keine kontaminierte Ladung die Detektoreffizienz beeinträchtigt. Der Testaufbau umfasst eine spezielle Leiterplatte (Hybrid 4.1). Darauf sind alle wesentlichen Elemente des Belle II Pixeldetektors wie DEPFET Sensor, Auslesechip (DCDB) und Steuerungschip (SwitcherB) installiert. Ein zwischengeschalteter Field Programmable Gate Array (FPGA) - ein programmierbarer Schaltkreis der Digitaltechnik - dient als Verbindung zum Computer. Experimentelle Ergebnisse dieser Masterarbeit lassen darauf schließen, dass der Gated-Mode-Betrieb auch bei der geplanten Zielfrequenz von 320 MHz ausgezeichnet funktioniert.

Contents 3

## **Contents**

| Abstract2 |                              |                     |                                               |    |  |  |

|-----------|------------------------------|---------------------|-----------------------------------------------|----|--|--|

| Cor       | ntents                       |                     |                                               | 3  |  |  |

| 1         | Intro                        | duc                 | tion                                          | 6  |  |  |

| 2         | Phys                         | Physics at Belle II |                                               |    |  |  |

|           | 2.1                          | 7                   |                                               |    |  |  |

|           | 2.2                          | В                   | ELLE II Detector System                       | 12 |  |  |

|           | 2.3                          | Sı                  | uperKEKB injection scheme                     | 14 |  |  |

|           | 2.                           | 3.1                 |                                               |    |  |  |

|           | 2.                           | 3.2                 | Beam Parameters increasing Luminosity         | 14 |  |  |

|           |                              | 3.3                 | Nano beam scheme                              |    |  |  |

|           | 2.                           | 3.4                 | Beam life time and dead-time during injection | 18 |  |  |

| 3         | DEPI                         | FET                 | Sensors                                       | 22 |  |  |

|           | 3.1                          | DI                  | EPFET Operation                               | 23 |  |  |

|           | 3.                           | 1.1                 | The DEPFET Principle                          | 23 |  |  |

|           | 3.                           | 1.2                 | Electrical properties of DEPFET devices       |    |  |  |

|           | _                            |                     | Readout of DEPFET Pixel Matrices              |    |  |  |

|           | _                            | 1.4                 | Clear Process                                 |    |  |  |

|           | 3.                           | 1.5                 | Parasitic Capacitances of a DEPFET Matrix     | 30 |  |  |

|           | 3.2                          | DI                  | EPFET Technology & Design                     | 30 |  |  |

|           | 3.3                          | Bi                  | asing scheme                                  | 31 |  |  |

|           | 3.4                          | Th                  | ne Gated Mode                                 | 34 |  |  |

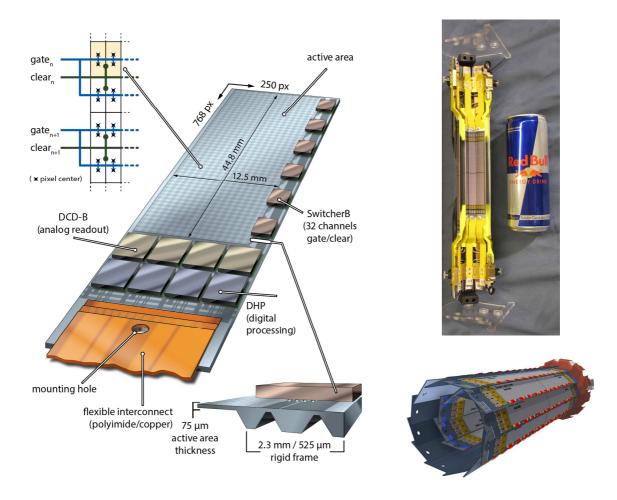

|           | 3.5                          | P                   | XD Detector                                   | 35 |  |  |

|           | 3.6                          | P                   | XD Sensor Electronics                         | 37 |  |  |

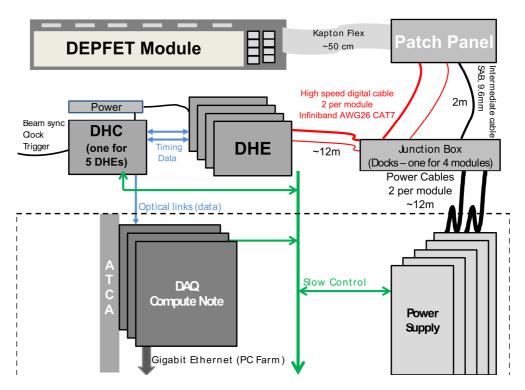

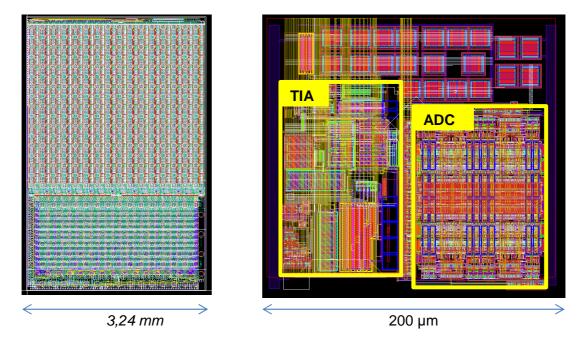

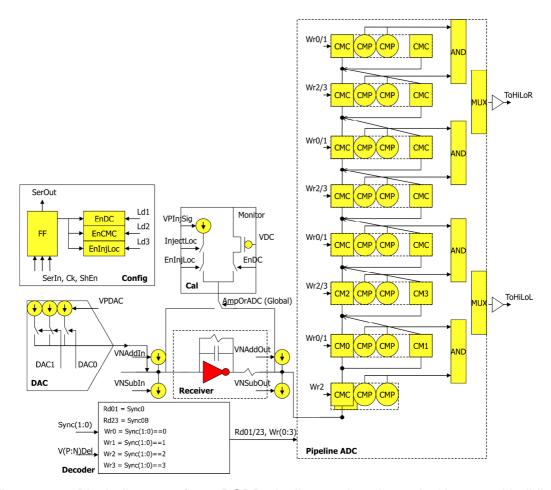

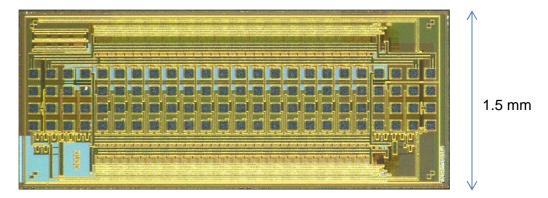

|           | 3.                           | 6.1                 | The DCDB pipeline                             | 38 |  |  |

|           | 3.                           | 6.2                 | Switcher-B                                    | 42 |  |  |

| 4         | Hybr                         | id 4                | .1 Board and FPGA Board                       | 45 |  |  |

|           | 4.1                          | O                   | verview                                       | 45 |  |  |

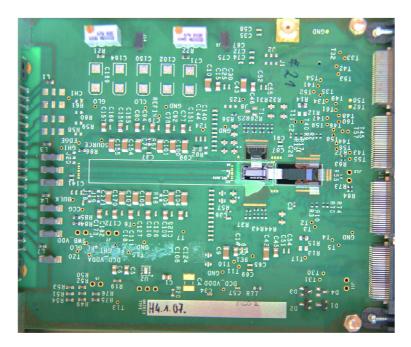

|           | 4.2                          | Ну                  | ybrid 4.1 Board                               | 46 |  |  |

|           | 4.3                          | FF                  | PGA Board                                     | 47 |  |  |

| 5         | Test Plan for the Gated Mode |                     |                                               |    |  |  |

| -         | 5.1                          | 5.1 Overview        |                                               |    |  |  |

|           | 5.2                          | Τe                  | esting of Hybrid4 PCB components              | 50 |  |  |

|           | _                            |                     | PXD6-Matrix                                   |    |  |  |

|           |                              |                     | DCDB pipeline Characterization                |    |  |  |

|           | 5.                           | 2.3                 | SwitcherB Characterization                    | 50 |  |  |

Contents 4

|      | 5.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | The Gated Mode Analysis                                      | 51  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-----|

| 6    | DCDB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | pipeline Characterization                                    | 52  |

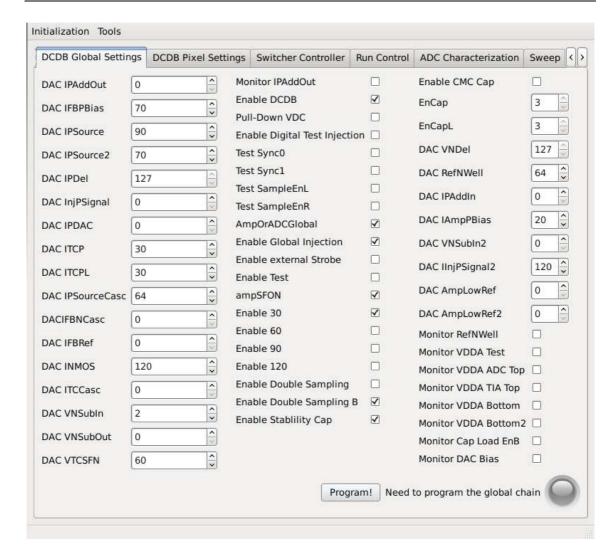

|      | 6.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | DCDB Test Software                                           | 52  |

|      | 6.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Digital functionality check                                  | 52  |

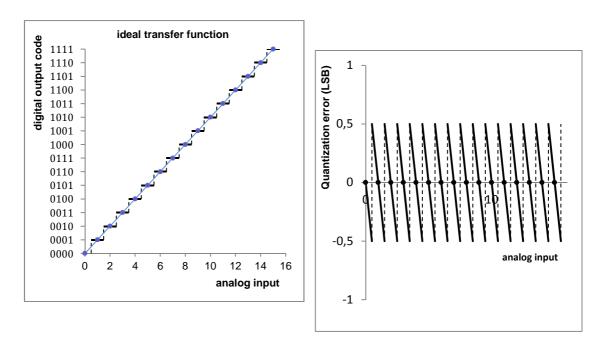

|      | 6.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Conversion Algorithm                                         | 53  |

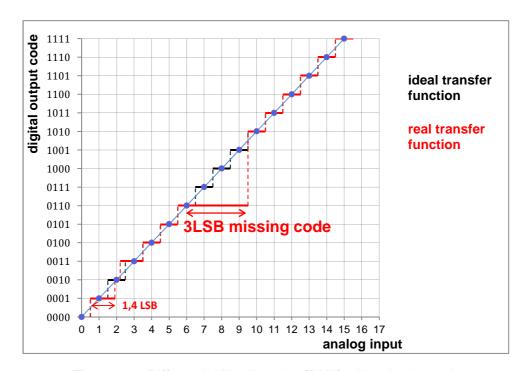

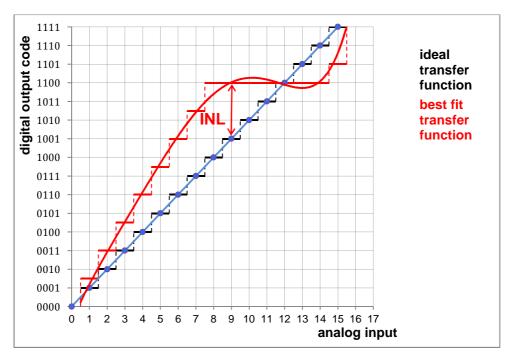

|      | 6.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ADC Error Sources                                            | 57  |

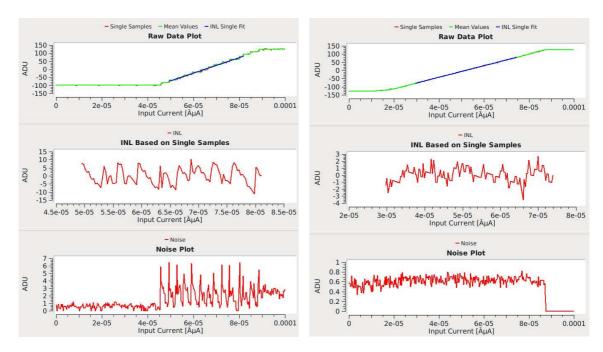

|      | 6.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ADC characterization                                         | 60  |

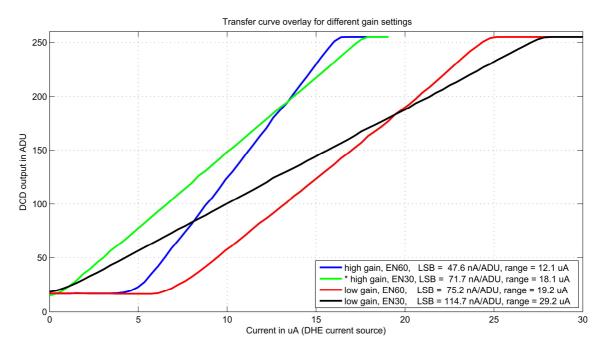

|      | 6.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5.1 Optimize Settings                                        | 60  |

|      | 6.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | .2 Analyzing the ADC Transfer Curves                         | 63  |

| 7    | The G                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ated Mode Operation                                          | 69  |

|      | 7.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Conceptual Approach for testing of the Gated Mode            | 69  |

|      | 7.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Processing Chain                                             | 70  |

|      | 7.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | .1 DEPFET Readout System                                     | 70  |

|      | 7.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | .2 The Gated Mode Analysis Tool                              | 70  |

|      | 7.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Programming Switcher Sequences                               | 74  |

|      | 7.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                              |     |

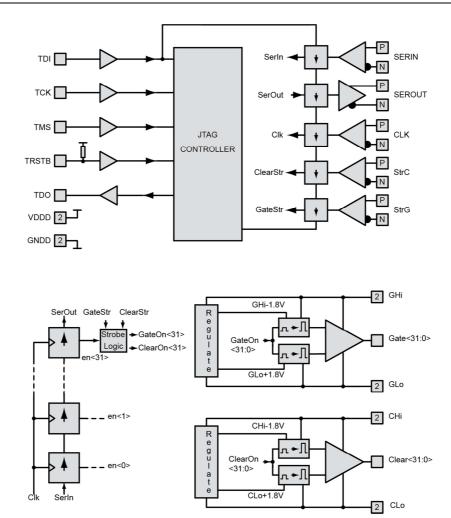

|      | 7.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3.2 SwitcherB Controller                                     | 79  |

|      | 7.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Calibration Measurement                                      | 80  |

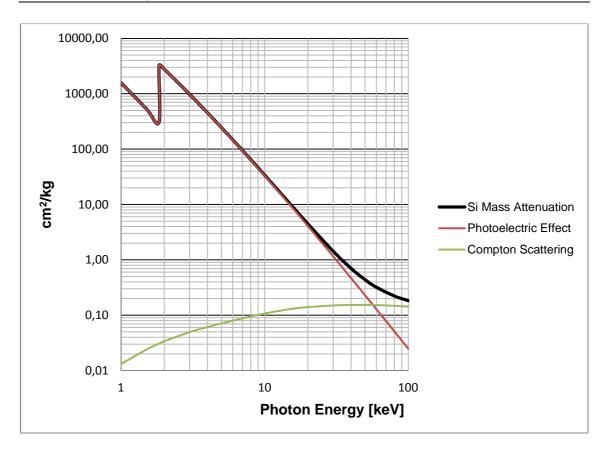

|      | 7.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | .1 Interaction of Photons with Silicon                       | 80  |

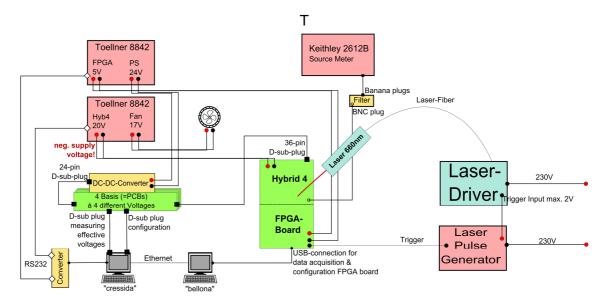

|      | 7.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | .2 Laser Intensity Measurements                              | 81  |

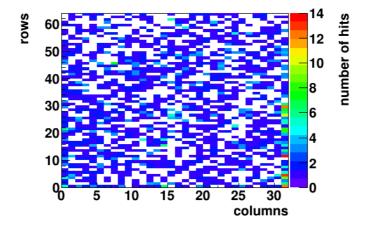

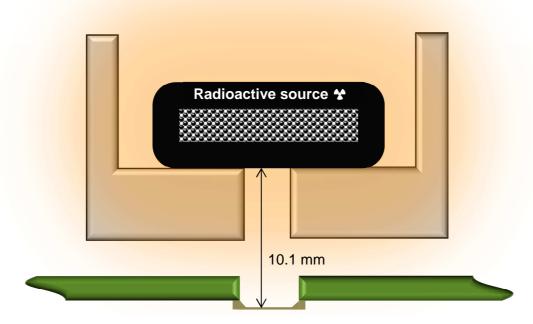

|      | 7.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | .3 Radioactive Source Measurements                           | 82  |

|      | 7.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | The Gated Mode Sequences                                     | 86  |

|      | 7.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | .1 Mapping                                                   | 86  |

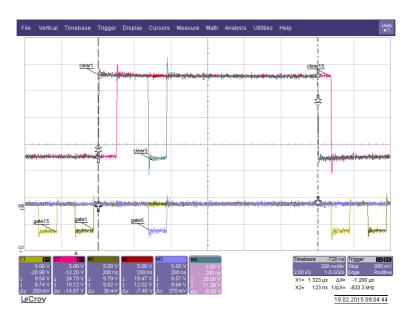

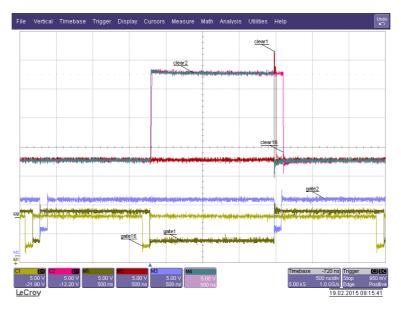

|      | 7.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6.2 Oscilloscope Measurements and Simulation of Strobe Logic | 86  |

|      | 7.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5.3 Experiment A: Signal Charge Preservation                 | 89  |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                              |     |

|      | 7.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5.5 Pedestal Analysis                                        | 94  |

| 8    | Resul                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ts                                                           | 99  |

| 9    | Concl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | usion and Outlook                                            | 101 |

| Appe | endix A:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | B-Meson Decay                                                | 103 |

| Арре | 7.3.1 SwitcherB Strobe Logic       74         7.3.2 SwitcherB Controller       79         7.4 Calibration Measurement       80         7.4.1 Interaction of Photons with Silicon       80         7.4.2 Laser Intensity Measurements       81         7.4.3 Radioactive Source Measurements       82         7.5 The Gated Mode Sequences       86         7.5.1 Mapping       86         7.5.2 Oscilloscope Measurements and Simulation of Strobe Logic       86         7.5.3 Experiment A: Signal Charge Preservation       89         7.5.4 Experiment B: Junk Charge Prevention       93         7.5.5 Pedestal Analysis       94         Results       99 |                                                              |     |

| Арре | endix C:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Radioactive Source Formulas                                  | 109 |

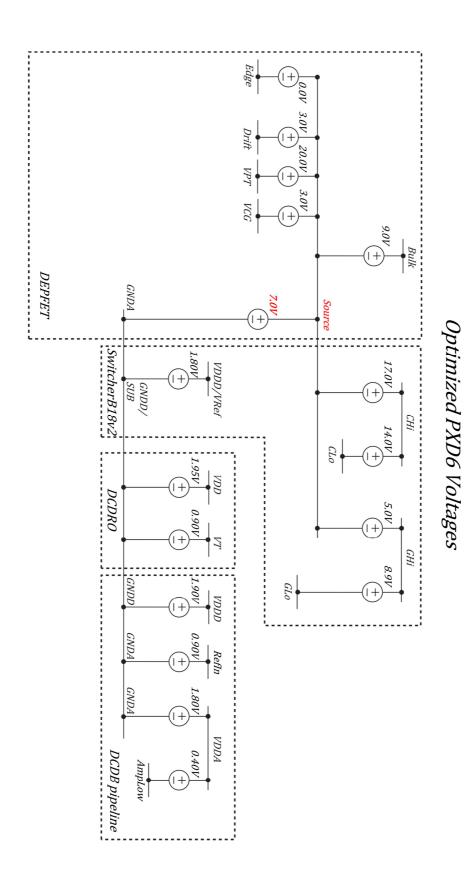

| Appe | endix D:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Optimized Test Setup Voltages                                | 111 |

| Appe | endix E:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SwitcherB Sequence Simulation                                | 112 |

| Glos | sary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                              | 115 |

| List | of Figur                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | es                                                           | 121 |

| List | of Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | S                                                            | 124 |

| <b>^</b> | _        |

|----------|----------|

| Contents | <b>h</b> |

| CONGING  | J        |

| Acronyms                   | 125 |

|----------------------------|-----|

| Bibliography               | 128 |

| Acknowledgement            | 136 |

| Declaration of originality | 137 |

1 Introduction 6

### 1 Introduction

Citius, altius, fortius, this principle not only governs the Olympic spirit but can also serve as a guideline for particle colliders. In spring 2015 after a two years break the LHC was upgraded to almost its full specified center of mass energy at 14 TeV. The electron positron community on the precision frontier will answer in 2017 with an upgrade of the KEKB collider ("Super-KEKB") at the KEK laboratory in Tsukuba (Japan).1 This collider will deliver an unprecedented luminosity of almost 10<sup>36</sup>/cm<sup>2</sup> and feature highly innovative technologies. Besides the revolutionary nano beam scheme a new ingenious DEPFET pixel detector ("PXD"), characterized by very low mass and internal amplification, will be inserted into the upgraded version of the Belle detector ("Belle II"), fitting perfectly the increased challenges. However, the thin DEPFET pixel sensors have to be read out sequentially row by row, resulting in a readout time of 20 us, which corresponds to two full turns of the particle bunches in the SuperKEKB rings. The continuous beam injection scheme of SuperKEKB implies for the PXD, that about 20% of all recordings should be spoiled by the huge background originating from the "cool down" of the injected daughter bunches ("noisy bunches"). This would mean a high waste of time and resources. Various scientific studies proved that DEPFET detectors are in principle capable of shielding or gating the sensor during the passage of the daughter bunches. The objective of this thesis is to optimize the Gated Mode operation so that it can be used at the full target frequency of 320 MHz.

Chapter 2 gives an overview of the physics pursued at "B-Factories" and motivates their benefits. Also the Belle II detector system and some beam peculiarities of SuperKEKB are briefly explained. Chapter 3 introduces the DEPFET detector together with its connected electronics and explains its working principles and special features including the Gated Mode. Chapter 4 describes the necessary components for the test setup whereas chapter 5 outlines a detailed test plan for the Gated Mode operation. Without properly operating electronics there is no way of getting meaningful findings. Therefore chapter 6 deals with the characterization of the readout chip and the determination of the optimal settings. Additionally, the conversion algorithm is explained and several potential error sources are investigated. Chapter 7 describes the data acquisition system and the programming of the test sequences in conjunction with a discussion to shed some light on the understanding of the digital strobe logic. Next the calibration method for the detector's output is illustrated and different Gated Mode sequences are evaluated. The results and conclusions are included in chapter 8 and 9, respectively. In order to facilitate the fluency of reading some terms marked in **bold** are not explained in the text but in the glossary at the end of this thesis.

<sup>&</sup>lt;sup>1</sup> and yet there are ongoing discussions for two Future Circular Colliders (FCCs), a proton-proton collider with a center of mass energy of 100 TeV and 80-100 km circular tunnel, as well as a >350 GeV high luminosity  $e^+e^-$  machine [116], besides two possible linear colliders, the ILC (at 500 GeV) [117] and CLIC (up to 3 TeV) [118]

## 2 Physics at Belle II

## 2.1 Basic Motivation: benefit of a Super Flavor Factory (SFF)

In 1972 Makoto Kobayashi and Toshihide Maskawa, two Japanese physicists, proposed a new scheme of the weak interaction of quarks, explaining the CP violation observed in the quark sector by Cronin and Fitch in 1964 [1]. This scheme postulates a CP violating phase and requires three families of quarks in the quark mixing matrix although at this time only three quarks (u, d and s) were known. The observed presence of CP violation in the B-meson system, detected by the BaBar² and Belle experiments, was an important confirmation of this hypothesis, awarding Kobayashi/Maskawa the Nobel Prize in Physics in 2008.

The name "Belle" stands for both an experiment in **flavor physics** conducted by the Belle collaboration and a detector system located at the collision point of the  $e^+e^-$  asymmetric energy collider, known as KEKB, in Tsukuba (Japan). The confirmation of the Kobayashi-Maskawa mechanism now widely accepted as the dominant source of CP violation in the Standard Model of particle physics (SM) was not the only outcome of the successful Belle experiment. Especially worth mentioning is the unprecedented precision with which the magnitudes of the CKM matrix elements and the angles of the unitarity triangle were extracted [2].

Nevertheless several fundamental questions in particle physics remain unanswered. Let me shortly describe a few of them: From the hot Big Bang model [3] one might expect that the universe consists of equal parts of matter and antimatter. However, the observed baryon asymmetry in the universe is by order of 10<sup>8</sup> higher than predicted by SM. While CP violation is an integral part of the SM framework and one of the so-called **Sakharov conditions** for a matter dominated universe, the magnitude of the asymmetry cannot be explained. A further mystery remains the cosmic observation of dark matter inferred from gravitational effects<sup>3</sup> on visible matter, cosmic microwave background analysis and the large-scale structure of the universe.

The recent discovery of a new particle with properties consistent with the SM Higgs boson at LHC was accommodated with great relief and big celebrations. Nevertheless the Higgs boson's mass is expected to be much heavier near the Planck scale [4]. Since the Higgs potential contains a term in the SM Lagrangian with quadratic mass divergence this means that the Higgs mass of  $\mathcal{O}(100 \text{ GeV})$  materializes only after a huge cancellation between the bare Higgs mass and the quadratic divergent mass renormalization [5]. This is often called the hierarchy problem occurring when funda-

<sup>&</sup>lt;sup>2</sup> BaBar represents an international collaboration of physicists located at SLAC National Accelerator Laboratory, operated by Stanford University for the Department of Energy in California

<sup>&</sup>lt;sup>3</sup> evidenced by galactic angular velocity distributions, gravitational lensing and galactic collisions

mental parameters of some Lagrangian are vastly different than the parameters measured by the experiment, in other words: the Higgs boson is much too light. One would expect that the large quantum contributions to the Higgs boson mass would inevitably make the mass huge, comparable to the scale at which new physics appears, unless there is an incredible fine-tuning cancellation between the quadratic radiative corrections and the bare mass. As an example let us use a top quark fermion loop for calculating the Higgs boson mass [6]:

Contributions from other fermions can be neglected. If we take for  $\Lambda^2$  the GUT scale then  $m_0$ , the uncorrected mass of the Higgs boson has to be determined with an accuracy of 24 digits in order to calculate a Higgs mass of 100 GeV associated with the first and second term from the SM Lagrangian (right part of the equation). It's hard to believe that such a fine-tuning is provided by nature.

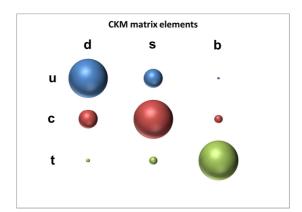

A further phenomenon currently not fully understood is related to the hierarchy of the CKM and the neutrino/lepton mixing matrix (PMNS) elements as shown in Figure 2-1. This again puzzles many physicists and points to some yet undiscovered mechanism existing at higher energy scales.

Figure 2-1: different weightings of CKM & PMNS matrix elements [7, 8]

In order to make considerable progress the Belle II collaboration is planning an upgrade for both the detector system and the collider<sup>4</sup> going live in 2017. With the emergence of the LHC operating at the TeV energy scale one might question the benefit of such Super Flavor Factories (SFF)<sup>5</sup> with energies still well below 100 GeV reaching not

<sup>&</sup>lt;sup>4</sup> now called SuperKEKB

<sup>&</sup>lt;sup>5</sup> often also referred to as B-Factories

even the mass of the Higgs particle quite recently detected. Moreover since the LHCb experiment is also studying flavor physics at much higher b-cross sections, it is understandable that for laymen in particle physics there are at least some doubts about the effectiveness of such enterprises. To answer these apparent inconsistencies one has to consider the goals pursued by the different approaches. The LHC is looking for new physics (NP) particles in high energy experiments by increasing the available center-of-mass energy whereas Belle II rather operating on the precision frontier would provide complementary constraints on the combination of couplings, mixing angles and NP masses [9].

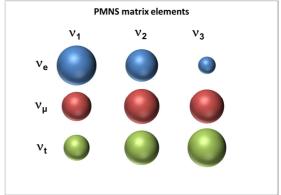

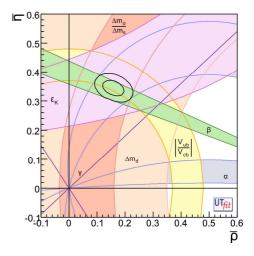

If direct searches for NP are successful (e.g. Supersymmetry) flavor experiments will deliver essential information to identify the kind of NP sensitive physics [10]. One of the most efficient ways achieving this goal is the comparison of the determined CKM parameters with SM predictions. This can be achieved by putting all experimentally obtained data together and applying a best-fit-algorithm<sup>6</sup>. Again one can imagine that these fits depend heavily on detailed calculations of the effects of radiative corrections. The main radiative effects arise from the influence of loop diagrams involving virtual heavy particle exchanges. Most of the performed measurements are related to specific regions in the  $\overline{\rho} - \overline{\eta}$  plane as shown in Figure 2-2.

Figure 2-2: Left: Regions corresponding to 95% probability for the CKM parameters  $\overline{\rho} - \overline{\eta}$  selected by different constraints, assuming present central values (summer 2014) with present errors. Right: zoomed in diagram representing 2007 fitting results.

Note that from the right plot of Figure 2-2 one can infer, that the uncertainty area was already small and a bold step towards increased integrated luminosity is needed to detect small deviations from the SM. This would dramatically change by placing a SFF into operation. In Figure 2-3 (left) based on 2007 data the validity of the SM is assumed applying the expected precision of a SFF. Going one step further and taking the current

<sup>&</sup>lt;sup>6</sup> currently two organizations take care of that: UTfit and CKMfitter with different statistical approaches (bayesian vs. frequentist approach) but there are also other methodologies like the Scan-Method [93]

world averages for all parameters with the expected precision of a SFF this diagram would have transformed to a paradigm of NP.

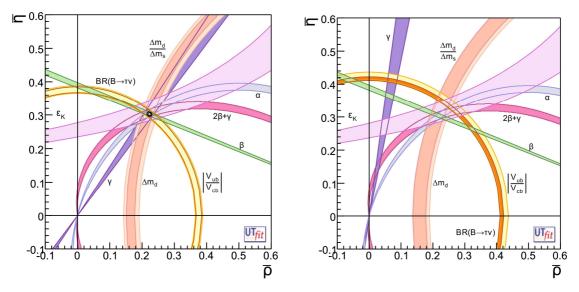

Figure 2-3: Left: Regions corresponding to 95% probability for the CKM parameters  $\overline{\rho} - \overline{\eta}$  selected by different constraints, assuming 2007 central values with errors expected at a SFF tuning central values to have compatible constraints. Right: assuming present central values with the precision of a SFF [11].

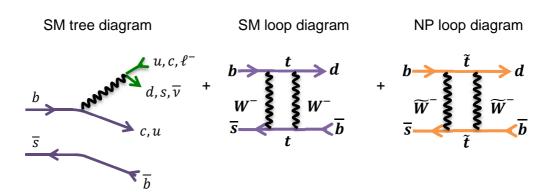

As an important tool for finding physics beyond the SM, flavor physics probes large mass scales via virtual quantum loops. FCNC, neutral meson-antimeson mixing and CP violation typically occur at the loop level in the SM. Precise measurements could potentially induce small NP virtual corrections. Hence this approach is also called indirect search for it infers NP through virtual contributions of new particles in processes involving only standard particles. It is based on high-statistics muon, kaon, tau, charm and B-meson production as well as precise measurements of SM parameters providing different constraints to individual processes. Experiments always measure the sum of SM and NP contributions. In order to set limits or to extract signals from NP it is indispensable to fully understand the underlying SM contribution. A widely accepted paradigm is that tree-level diagrams are dominated by SM processes, whereas loop diagrams can be strongly influenced by NP [12]. An example is given in Figure 2-4.

Figure 2-4: Example of an SM standard process and 1<sup>st</sup> order loop corrections

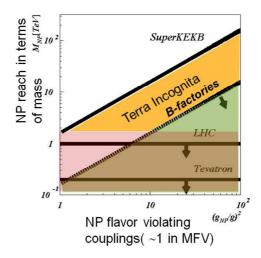

Both loop diagrams would add in the amplitude and hence interfere. The inclusion of NP particles with mass exchanged at the tree level with  $\mathcal{O}(1)$  coupling constants  $g_{NP}/g$  would go well beyond the LHC energy scale [9]. Even if NP particles are exchanged only at 1-loop order the mass reach can be as high as  $\mathcal{O}(1\text{TeV/c}^2)$  if **minimal flavor violation** (MFV) is assumed [13], and up to  $\mathcal{O}(100\text{TeV/c}^2)$  if flavor violation couplings are enhanced compared to the SM [11]. The scope of the two approaches in searching for NP is depicted in Figure 2-5.

Figure 2-5: Sensitivity to New Physics as a function of the flavor violating couplings relative to the SM in the indirect searches at KEKB/SuperKEKB and direct searches at LHC/Tevatron [14].

In general if NP appears at the TeV scale in LHC experiments, SuperKEKB could measure its flavor- and CP-violating couplings or set independent constraints on the NP Lagrangian [15]. A comparison of SuperKEKB with **LHCb** unveils that the strengths of the two experiments are largely complementary [9]. At LHCb the expected yield for decay processes like B  $\rightarrow$  K\*µµ, B<sub>s</sub>  $\rightarrow$   $\phi\phi$  and B  $\rightarrow$   $\phi$ K<sub>s</sub> should be substantially higher [16] because of the very large production cross section for b-quarks. This allows for example, extensive studies on B<sub>s</sub> meson oscillations. On the other hand SuperKEKB provides a much cleaner environment which is essential for the exact measurement of CKM matrix elements, rare decay modes with missing energy as well as other searches for possible NP effects [2].

Colliders at Super Flavor Factories can form specific particles or their excitations without any associated particles in the form of resonances. As an example at the  $\Upsilon(4S)$  resonance  $B\overline{B}$ -pairs are generated. This allows the full reconstruction of a B meson from its daughter particles. By this means one can infer the missing momentum attributed to the other B meson, which in turn is essential for the measurement of channels including neutrinos in the final state.

## 2.2 BELLE II Detector System

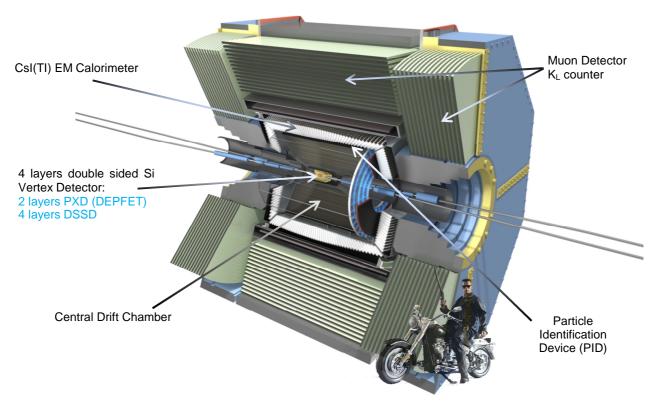

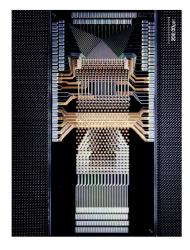

Detectors employed in high energy physics experiments normally incorporate several types of detection techniques into one single detector system [17]. The Belle II detector system in Figure 2-6 shows also a general purpose spectrometer consisting of layers of sub-detector components, each designed to look for particular properties or specific types of particles, arranged in the typical "onion shell"-fashion [18, 19]:

Figure 2-6: Belle II Detector System

There are tracking devices recording position, arrival time and path of a particle, calorimeters that measure a particle's energy, and particle-identification detectors using a range of techniques to pin down a particle's identity.

VerteX Detector (VXD): positioned most closely to the beam pipe there are two layers of Pixelated Silicon Sensors (PXD) adjacently followed by four layers of double-sided Silicon Strip Sensors (SVD). Together this sub-system measures decay vertex positions with a combined impact parameter resolution of σ<sub>z0</sub> ~ 20μm [19]. The precise evaluation of position coordinates is necessary for the determination of the particle's trajectory origin. These tracking detectors register tiny electrical signals that particles create traversing the detector. From the deflection in a magnetic field the particle's momentum can be derived. One of the main concerns for the Belle II collaboration is the detector performance in an environment with considerable higher background levels. Conservative estimates assume that the background hit rate will increase by a factor of 20 whereas the physical event rate will be about 50 times higher. In this respect

the addition of a pixel detector is essential since results from current flavor factories have proven high precision vertex reconstruction as a powerful tool to measure CP violation observables [20].

- Central drift chamber (CDC): the VXD is surrounded by a small-cell drift chamber (r = 16 112 cm) which measures trajectories, momenta and dE/dx information of charged particles. Additionally, it is used as trigger source and as a particle identification device for low momentum tracks.

- Particle Identification Device (PID): located just outside of the CDC in the barrel and end cap regions and principally<sup>7</sup> designed to improve the  $K/\pi$  separation capability of the detector [10]. They are of the **Cherenkov** type with very fast read-out electronics. In the barrel region the formerly used ARICH counters are replaced by Time-Of-Propagation (TOP) counters allowing to measure the propagation time of the Cherenkov light emitted from charged particles passing through quartz radiator bars. In order to identify charged particles over the full kinematic range this detector sub-system also includes a forward end cap RICH with an aerogel radiator.

- Electromagnetic calorimeter (ECL): photons generated by e<sup>+</sup>e<sup>-</sup> collisions at the Y(nS) energy regime span a wide energy range from 20 MeV to 4 GeV, hence a high resolution electromagnetic calorimeter is essential for the precise determination of the photon energy and angular coordinates. It contains a total number of 8736 CsI(TI)-scintillator crystals with different shapes in the barrel and end cap region located inside a Superconducting Solenoid Coil that provides a 1.5 Tesla magnetic field.

- K<sub>L</sub>/Muon (KLM) Detector: the outermost detector sub-system is instrumented to detect K<sub>L</sub><sup>0</sup> mesons and to identify muons. It consists of an alternating "sandwich" of 4.7-cm thick iron plates<sup>8</sup> and glass-electrode Resistive Plate Chambers (RPC) in between. Since RPCs in the innermost layers of the KLM detector show unsatisfactory performance in the end cap region because of the expected high background, they are replaced with scintillators.

There are many other factors influencing the performance of the Belle II detector system. Especially worth mentioning are a fast and reliable Triggering scheme (TRG), a Data Acquisition system (DAQ) recording collision events of interest upon trigger level-1 and a grid-based distributed computing facility for data processing, MC production and physics analysis.

<sup>&</sup>lt;sup>7</sup> Providing also discrimination between pions, kaons and electrons below 1 GeV/c

<sup>&</sup>lt;sup>8</sup> serving as stopping material and as the magnetic flux return for the solenoid

## 2.3 SuperKEKB injection scheme

#### 2.3.1 Principles of particle acceleration

In order to accelerate particles in a synchrotron and to compensate for energy losses due to the emission of synchrotron radiation a longitudinal electric field is needed. Radiofrequency (RF) cavities<sup>9</sup> along the beam pipe use an oscillating voltage, so the particle senses an accelerating electrical field in the cavities. To ensure that a charged particle always receives an accelerating force within the cavity, the RF frequency must be an integer multiple of the particle's revolution frequency [21]:

$$h(integer) = harmonic number = \frac{RF frequency}{revolution frequency}$$

(2-1)

At SuperKEKB the planned RF frequency basis clock is 508.89 MHz. With a circumference of 3 km the harmonic number for electrons at the speed of light gives about 5120 points.<sup>10</sup> The segments of the circumference centered on these points are called RF buckets. Electrons within the RF buckets get lumped into bunches.<sup>11</sup> Each bunch consists of 10<sup>11</sup> positrons or electrons. The particle density within a bunch is not homogeneous but looks like a 3-dimensional Gaussian distribution.

The electrons in a bunch oscillate longitudinally around the equilibrium position, keeping the longitudinal size of the bunch stable. These oscillations are called synchrotron oscillations [18].

The electrons and positrons are guided in SuperKEKB by magnetic dipole fields around circular orbits, but move sinusoidally in both horizontal and vertical planes under focusing magnetic quadrupole fields around the design orbit. These periodic lateral movements are called **betatron** oscillations.

#### 2.3.2 Beam Parameters increasing Luminosity

SuperKEKB is an asymmetric  $e^+e^-$  collider with a planned target luminosity of  $\mathcal{L}=8x10^{35}cm^{-2}s^{-1}$ , about 40 times as high as its predecessor KEKB [22, 23]. The range of beam energy covers the  $\Upsilon(1S)$  and  $\Upsilon(6S)$  resonance states for the physics operation. By definition luminosity<sup>12</sup> is related to the rate of particle collisions, consequently it is crucial for the production of meaningful quantities of rare events. The number of detected events N depends on the process cross section  $\sigma$  usually measured in femto-

<sup>&</sup>lt;sup>9</sup> metallic chambers containing an electrical field in order to accelerate charged particles

with this number one can calculate the bucket length of ≈59 cm, which has to be compared with a bunch length of just 5-6 mm at SuperKEKB

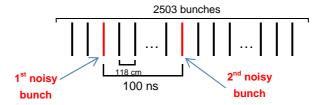

<sup>&</sup>lt;sup>11</sup> this represents also an upper limit for the number of bunches within the collider (at Belle II only every second bucket gets filled with electrons resulting in 2503 bunches altogether)

<sup>&</sup>lt;sup>12</sup> luminosity can be interpreted as the beam focusing ability of the machine at the interaction point

barns<sup>13</sup> (fb) or picobarns (pb), the luminosity  $\mathcal{L}$  controlled by the beam parameters of the collider and the detector efficiency  $\epsilon$  including trigger efficiency:

$$\frac{dN}{dt} = \mathcal{L} \cdot \sigma \cdot \epsilon \tag{2-2}$$

The event rate  $N_{ev}$  of a specific process is given as:

$$\frac{dN_{ev}}{dt} = \mathcal{L} \cdot \sigma_{ev} \cdot Br \cdot \epsilon \tag{2-3}$$

where Br is the branching ratio, i.e. the fraction of events for a chosen particle measured to decay in a certain way<sup>14</sup> and  $\sigma_{ev}$  the cross-section dependent on the specific physics process only. Unfortunately with higher luminosity new phenomena emerge at the interaction point (IP) [24]: dynamic beta effects and disruption are just some of them and will not be further covered in this thesis.<sup>15</sup>

In common textbooks luminosity for two transverse Gaussian beam distributions colliding head-on with equal beam sizes is defined as

$$\mathcal{L} = \frac{f N_1 N_2}{4\pi \sigma_x^* \sigma_y^*} \tag{2-4}$$

where f is the bunch collision frequency,  $N_{1,2}$  the number of particles per bunch in beam<sub>1,2</sub> and  $\sigma_{x,y}^*$  is the beam size at the IP in the horizontal and vertical plane.

When the vertical **beta functions** of both beams are equal, the luminosity can be alternatively expressed by beam parameters (2-5) [25]:

$$\mathcal{L} = \frac{\gamma_{\pm}}{2er_e} \left( 1 + \frac{\sigma_y^*}{\sigma_x^*} \right) \left( \frac{I_{\pm} \xi_{y\pm}}{\beta_y^*} \right) \left( \frac{R_L}{R_{\xi y\pm}} \right) \propto \frac{I_{\pm} \xi_{y\pm}}{\beta_{y\pm}^*}$$

(2-5)

where the subscript  $\pm$  denotes positrons and electrons,  $\gamma_{\pm}$  is the Lorentz factor, e is the elementary electric charge,  $r_e$  is the classical electron radius, I is the beam current,  $\xi_{\pm}$  is the vertical beam-beam parameter,  $\beta_{y\pm}^*$  is the vertical beta function,  $R_L$  and  $R_{\xi y\pm}$  are geometrical reduction factors for the luminosity and the vertical beam-beam tune-shift parameter, respectively, owing to the finite crossing angle and the **hourglass effect**. Other factors like the horizontal beta function at the IP, the horizontal **emittance**  $\varepsilon_{xy}$ , the bunch length and the crossing angle between two beams not directly appearing in

<sup>14</sup> the sum of branching ratios for a particle is 1

$<sup>^{13}</sup>$  1 barn =  $10^{-28}$  m<sup>2</sup>

<sup>&</sup>lt;sup>15</sup> the high density of compressed particles provides strong electromagnetic fields viewed by the particles of the incoming beam and this would bend particle trajectories (disruption)

<sup>&</sup>lt;sup>16</sup> the star indicates the minimum value

the formula are contributing to the luminosity through the beam-beam parameter [26]. Table 2-1 gives an overview of some key design parameters for KEKB/SuperKEKB.

|                               | KEKB design | KEKB with crab | SuperKEKB <sup>17</sup> | Unit                                              |

|-------------------------------|-------------|----------------|-------------------------|---------------------------------------------------|

| Energy                        | 3.5/8       | 3.5/8          | 4.0/7.0                 | GeV                                               |

| $oldsymbol{eta_y^*}$          | 10/10       | 5.9/5.9        | 0.27/0.3                | mm                                                |

| $oldsymbol{eta}_x^*$          | 330/330     | 1200/1200      | 32/25                   | mm                                                |

| $oldsymbol{arepsilon}_{\chi}$ | 18/18       | 18/24          | 3.2/5.3                 | nm                                                |

| $\sigma_x^*$                  | 100         |                | 10                      | μm                                                |

| $\sigma_y^*$                  | 1.9         | 0.94           | 0.048/0.062             | μm                                                |

| $\xi_y$                       | 0.052       | 0.129/0.090    | 0.09/0.081              |                                                   |

| $\sigma_z$                    | 4           | 6-7            | 6/5                     | mm                                                |

| I                             | 2.6/1.1     | 1.64/1.19      | 3.6/2.6                 | А                                                 |

| $N_{bunch}$                   | 5000        | 1584           | 2503                    |                                                   |

| Luminosity                    | 1           | 2.11           | 80                      | 10 <sup>34</sup> cm <sup>-2</sup> s <sup>-1</sup> |

Table 2-1: Comparison of some of the key parameters of the SuperKEKB and KEKB designs [25]. Figures in bold red indicate three fundamental parameters determining luminosity.

#### 2.3.3 Nano beam scheme

From equation (2-5) one can infer that the luminosity is sensitive to only three fundamental beam parameters:<sup>18</sup>

- increase the beam currents (*I*<sub>+</sub>),

- make the electromagnetic beam-beam interactions small or equivalently increase the beam-beam parameter  $(\xi_{y\pm})$  which is inversely proportional to the beam emittance [27] and

- reduce the vertical beta function  $(\beta_{y\pm}^*)$  which addresses the focus of the beams at the interaction point [28].

Beam currents at SuperKEKB will be doubled in comparison with KEKB thus obtaining a luminosity gain by a factor of 2. Further current increases are not recommendable because of the electron cloud effect in the positron ring, high power costs and much higher detector backgrounds.

Regarding the beam-beam parameter, experiences from various colliders show that this value is limited to about 0.02-0.1. At SuperKEKB a maximum of 0.09 is assumed which has been already achieved at KEKB.

<sup>&</sup>lt;sup>17</sup> as of 2013/July/29

<sup>&</sup>lt;sup>18</sup> as an intermediate step KEKB scientists have installed crab cavities kicking the head and tail of each electron bunch so that the bunches made effective head-on collisions at the interaction point instead of crossing at an angle of 1.3 degrees (crab crossing improved the luminosity by 15%)

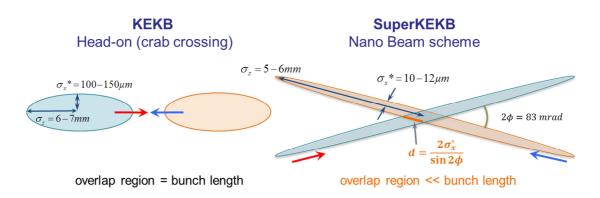

The most important luminosity increase will be achieved with a concept called "nano beam scheme" first proposed by scientists planning for the ILC [29]. The principal idea behind the nano beam scheme is to make the bunches very flat<sup>19</sup> in this way raising the collision probability. At SuperKEKB the vertical beta function  $\beta_y^*$  will be compressed by a factor of 1/20 of KEKB to just a few hundred microns at most. The new design will need strong final focusing quadrupole magnets placed closer to the interaction region to squeeze the beam into narrower bunches. However, this cannot be done arbitrarily small because of the **hourglass effect**. To minimize the hourglass effect for conventional head-on collisions the beta function has to be larger than the bunch length ~5mm  $(\beta_y^* \ge \sigma_z)$ . By contrast the nano beam scheme requires  $\beta_y^* \ge \frac{2\sigma_x^*}{\sin 2\phi}$  disclosing a proportional dependence on the horizontal spot size and an inverse dependence on the half crossing angle  $\phi$ . Accordingly the crossing angles will be substantially enlarged from 22 mrad to 83 mrad and the bunches only intersect at the highly focused regions with effective bunch length  $d = \frac{2\sigma_x^*}{\sin 2\phi}$  shown in Figure 2-7.

Figure 2-7: Comparison of different Collision Schemes (schematic view)

In order to implement the new scheme effectively a lot of former used items of the KEKB collider have to be upgraded [25]. First of all the lattice design, which represents the arrangement of the magnets along the beam path for guiding and focusing the electrons and positrons has to be updated. The magnet system in accelerators consists of various types like dipoles used for bending, quadrupoles used for focusing (focusing in one plane, and defocusing in the other) and sextupoles used for chromatic corrections. The combination of different magnets into building blocks constitute the lattice design resembling a complicated optical system with FODO cells (focusing & defocusing quadrupoles), double bend achromat (DBA), triple bend achromat (TBA) or other multi bend achromat types. For SuperKEKB the quadrupole magnets of KEKB will be reused as much as possible, the dipole magnets will be replaced by shorter ones and the period of the **wiggler magnets** will be reduced to half of that of KEKB by adding new ones. As already mentioned the final focus section was completely redesigned to achieve an extremely low beta function at the IP. By rearranging, replacing and adding magnets

<sup>19</sup> one might think of steamrolled spaghettis

-

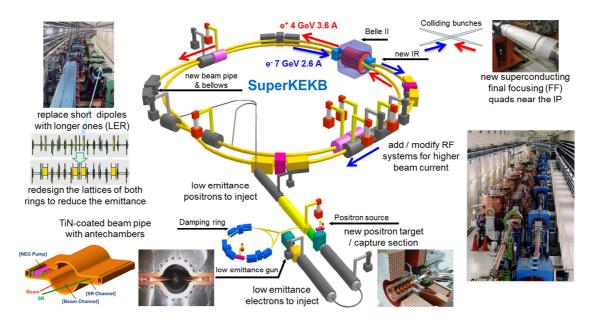

the beta functions and dispersions will be modified. As a countermeasure against electron cloud issues the beam pipes in the LER arc section will be replaced with new aluminum-alloy pipes with antechambers. To reduce the emittance of the electron beam a photo-cathode RF low-emittance electron gun will be installed. The emittance of the positron beam will be minimized by a new damping ring. The overview of the upgrade to SuperKEKB is shown in Figure 2-8.

Figure 2-8: Overview of upgrade to SuperKEKB [25]

#### 2.3.4 Beam life time and dead-time during injection

Due to various energy loss effects (see below), some of the particles deviate from the prescribed path along the vacuum tube and interact with the beam pipe thereby creating particle showers which may reach the detector. The number of particles lost in an accelerator is proportional to the number of beam particles [30]:

$$dN = -\alpha N(t)dt \tag{2-6}$$

where  $\alpha$  is a constant. Defining the beam lifetime as  $\tau = 1/\alpha$ , then the beam current I decays as

$$I = I_0 \cdot e^{-t/\tau} \tag{2-7}$$

In general, beam losses mainly arise in the collimation area or on other aperture limits. Basically five beam loss processes are observable [31]: first, betatron or synchrotron oscillations intensify the quantum emission thereby increasing the tails of the bunch distribution. Next, the intra-beam scattering dominated by the **Touschek effect**, and the beam-beam background appearing at the IP when the colliding beam particles undergo scattering via radiative **Bhabha** processes. Finally, elastic and inelastic scattering with residual gas molecules in the vacuum tube.

The individual loss mechanisms contribute to the total beam lifetime as [32]:

$$\frac{1}{\tau} = \frac{1}{\tau_{quantum}} + \frac{1}{\tau_{Touschek}} + \frac{1}{\tau_{beam-beam}} + \frac{1}{\tau_{elastic}} + \frac{1}{\tau_{inelastic}}$$

(2-8)

As a result the total beam lifetime will always be less than the value of the smallest lifetime input. The most dominant beam loss contribution stems from the Touschek effect. The stability of the trajectories highly depends on the amplitudes of betatron and synchrotron oscillations. If these oscillations are outside the longitudinal or transverse acceptance of the storage ring the particles are lost. In this respect it is customary to define dynamic aperture as the maximum phase-space amplitude within which particles do not get lost after a certain amount of turns<sup>20</sup> [33]. In other words, dynamic aperture sets an amplitude threshold for the motion of charged particles. At SuperKEKB it is estimated numerically with six-dimensional tracking simulations using a specific program for optics design and particle tracking. As a result the dynamic aperture is rather small compared to KEKB inducing a larger background and consequently a shorter lifetime of the beam. The intra-beam scattering rate ("Touschek effect") per particle depends on the following parameters [34]:

$$(Rate) \propto \frac{N}{E^3 \cdot \sigma} \tag{2-9}$$

where N stands for the number of particles per bunch, E for the beam energy and  $\sigma$  represents the transverse beam size. As already mentioned most of the luminosity increase at SuperKEKB comes from a significant reduction of the beam size. A twenty-fold compression of the bunches significantly rises the likelihood of intra-bunch coulomb scattering. By implication this increases the amplitudes of particles that will be either absorbed at the collimation area or collide with the beam wall. Accordingly, the dominant particle loss mechanism<sup>21</sup> at Belle II will be the Touschek effect reducing the LER beam lifetime significantly from 150/200 min as in the KEKB case to just 10 min. As a consequence the bunches have to be replenished continuously. This is done by injecting two "daughter bunches" 100 ns apart into the LER and HER respectively at a total frequency of 50 Hz. The pair of daughter bunches are selected by bunch current monitors, and the pair with the smallest bunch current sum is chosen to be topped off in the next injection.

-

<sup>&</sup>lt;sup>20</sup> 1000 turns at SuperKEKB with synchrotron oscillation but without **quantum excitation (radiation damping)**

<sup>&</sup>lt;sup>21</sup> the loss rate due to scattering with gas molecules is lower by a factor of 3-4

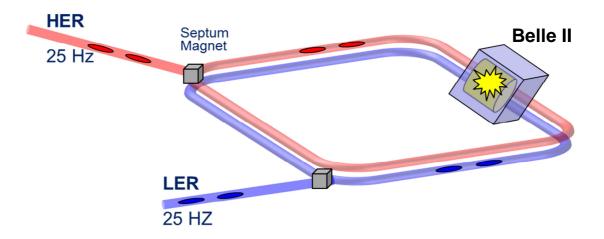

Figure 2-9 and Figure 2-10 give an overview of the injection scheme for SuperKEKB with the septum magnets for bunch injection.

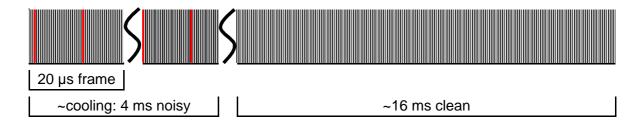

Figure 2-9: SuperKEKB bunch train.

Figure 2-10: Injection Scheme of SuperKEKB

Now the problem emerges that these daughter bunches are located further away from the orbit of the corresponding main bunches and therefore are subject to large amplitudes in their betatron oscillations. They are naturally cooled down by synchrotron radiation within a certain damping time. During this time the particles in the daughter bunches are more likely to collide with the bream pipe in the vicinity of the interaction point, creating additional background. The daughter bunches are therefore often called "noisy bunches". At KEKB the damping time was 4 ms and this number will be also assumed for SuperKEKB. The noisy bunches will pass the detector every 10 µs. For the PXD (see chapter 3.5) the detector readout cycle was determined at 20 µs which means that all signals registered within the 20 µs between two readout cycles are

stored (integrated). As a worst case this would mean that all frames recorded during the cooling period have to be discarded. This would substantially raise the dead-time of the detector to 20% or in other words produce a loss of two years time assuming a typical operational period of 10 years. Many proposals have been made to overcome this problem, for example a faster read-out (4-fold ganging), decreasing the injection rate while injecting 4 bunches instead of 2, synchronize injections from LER and HER or reducing damping time. But these alternatives are either too costly or not feasible from the current technical status. Fortunately the PXD used at Belle II offers a lot of amazing features especially the possibility to gate the detector during the passage of the noisy bunches. Its modalities, operation principles and the design will be described in the next section.

#### 3 DEPFET Sensors

Flavor physics sets high standards on precision measurements requiring a spatial resolution of a few ten of microns in order to measure the decay vertices of the two B mesons produced at the  $\Upsilon(4S)$  resonance. At Belle II a specific condition for detector resolution is the measurement of the decay time difference of the B meson and its antiparticle, expressed in their mean flight distance of  $\Delta z \approx 130~\mu$ . A derivation of this figure can be found in the Appendix A.

To safely distinguish two different vertices the vertex resolution has to be one order of magnitude better than the distance between the vertices [35]. Only silicon detectors can meet the challenge of acceptable resolution combined with a fast readout. However, the double sided silicon strip detector (DSSD) as innermost detector used for Belle cannot cope with the much higher event rate at SuperKEKB together with the higher background<sup>22</sup>, which would lead to a large strip **occupancy** making vertex reconstruction of B-decays impossible. For that reason it was decided to upgrade the new Belle II detector system with a pixel detector. The combined PXD and SVD **impact parameter** resolution at Belle II will be at  $\sigma_{z_0} \approx 20 \ \mu m$ .

There are fairly different pixel detector architectures under consideration all having advantages and drawbacks [36]. CCDs suffer from relatively slow read-out speed and continuous sensitivity distorting the measurements during the transfer cycle. In contrast hybrid pixels used for the ATLAS detector at CERN are very fast (25 ns read-out speed) but with their thick sensors and chip-integrated full read-out electronics they are too bulky for energy levels in the O(1GeV) area (multiple scattering because of relatively low particle momentum). A very promising and highly innovative technology are monolithic active pixel sensors (MAPS) incorporating standard CMOS technology in a p-type epitaxial layer on a high resistive n-type substrate [37]. Because of their low intrinsic capacitances these devices have excellent signal to noise ratios. On the other hand the charge collection times are still too long. Nevertheless the idea of integrating readout electronics into a single monolithic device will influence the construction of detectors in future high energy experiments. In contrast DEPFET detectors seem to be actually best-suited for high precision vertex pixel detectors [38]. They avoid most of the above shortcomings having low mass and offering intrinsic amplification and adequately fast readout times. Furthermore power consumption can be kept very small saving additional cooling material.

<sup>&</sup>lt;sup>22</sup> the beam pipe radius shrinks to about 10 mm, so the detector can be put closer to the IR, which is good news for vertex reconstruction; on the other hand the background increases substantially since is proportional to the inverse square of the radius

## 3.1 **DEPFET Operation**

#### 3.1.1 The DEPFET Principle

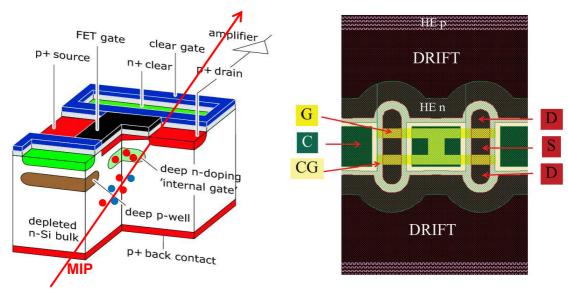

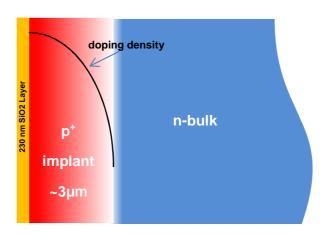

The idea for DEPFET detectors was proposed by two Munich scientists J. Kemmer and G. Lutz in 1987 [39]. The technology was developed by the Semiconductor Laboratory (HLL) of the Max Planck Society in Munich. DEPFET detectors integrate signal detection and first amplification in a single silicon pixel structure, so that the position measurement of traversing particles can be achieved with a minimum of material. The sensor consists of a depleted p-channel MOSFET implanted onto the surface of a high-resistive n-doped silicon substrate and a p<sup>+</sup> implant at the backside. More about semi-conductor devices can be found in common textbooks like [40, 36], MOSFETs are comprehensively described in [41].

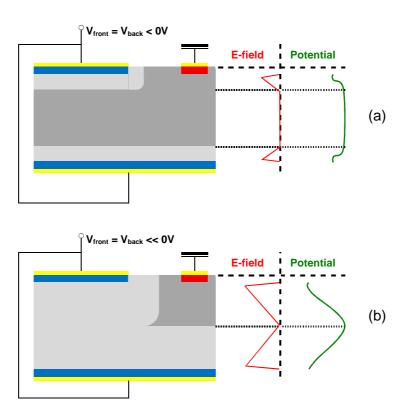

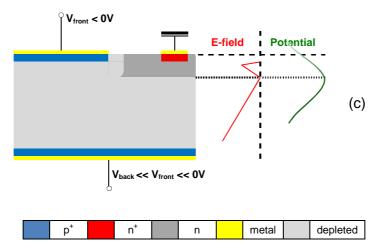

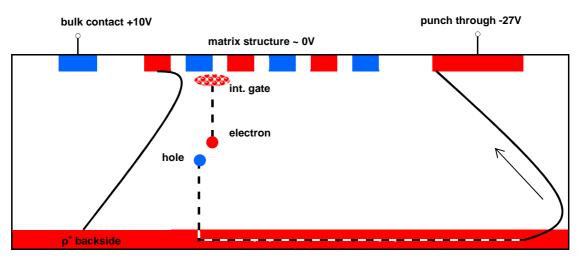

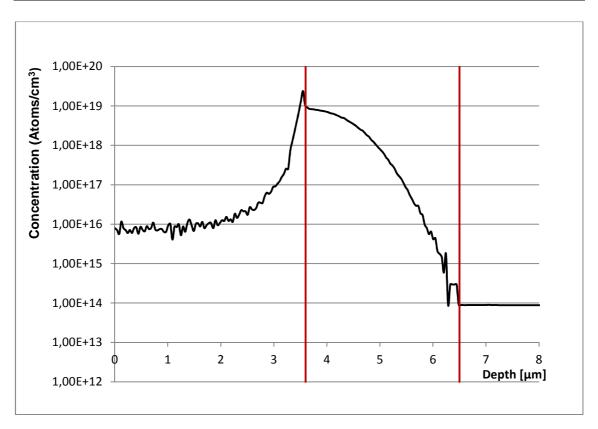

The substrate is fully depleted by means of sideward depletion as depicted in Figure 3-1. This is established by applying negative voltages to the source  $p^+$  and back contact  $p^+$  relative to the bulk potential  $n^+$  (a). If the voltages applied on both  $p^+$  contacts are sufficiently strong and equal, the depletion layers will meet in the center of the substrate (b) creating a potential minimum for the electrons. By relatively varying back and front side voltages, the minimum is shifted up vertically right below the top surface of the bulk substrate (c).

Figure 3-1: Concept of sideward depletion. Two p-n junctions share the same bulk contact. The n-bulk is grounded by means of a n<sup>+</sup> electrode. The electrical field and the parabolic potential curves for different voltage settings are displayed on the right.

The full depletion voltage  $V_{dep}$  of an n-type bulk together with a highly doped p<sup>+</sup> region is directly proportional to the quadratic sensor thickness  $d^2$  [36]:

$$V_{dep} + V_{bi} = \frac{q}{2\varepsilon\varepsilon_0} d^2 |N_{eff}|$$

(3-1)

with  $V_{bi}$  the **built-in** voltage representing the potential difference across the p-n junction in equilibrium, q the elementary charge,  $\varepsilon$  the vacuum permittivity and  $\varepsilon_0$  the relative permittivity of silicon and the effective doping concentration  $N_{eff} = \frac{N_A \cdot N_D}{N_A + N_D}$  with  $N_A$ ,  $N_D$  the acceptor and donor concentrations.

The position of the potential minimum  $z_{min}$  can be derived solving the one-dimensional Poisson equation with the given boundary conditions  $(\varphi(0) = V_{front}, \varphi(d) = V_{back})$  [42]:

$$z_{min} = \frac{d}{2} + \frac{\varepsilon \varepsilon_0}{q N_D d} \left( V_{back} - V_{front} \right)$$

(3-2)

where it was assumed that the acceptor concentration is much larger than the donor concentration  $N_A \gg N_D$ .  $V_{back} - V_{front}$  label the voltages of the back and front side p<sup>+</sup> electrodes.

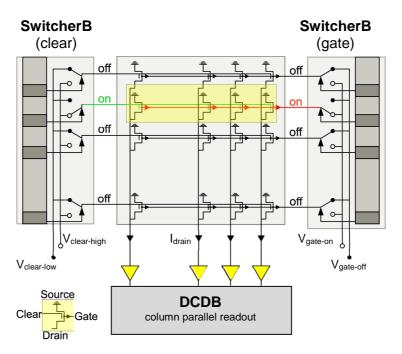

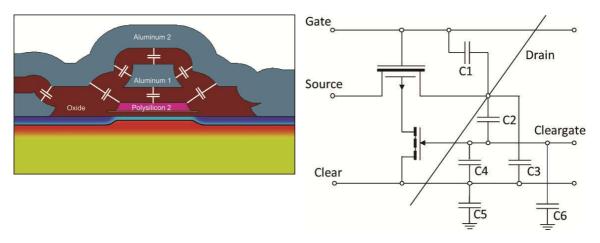

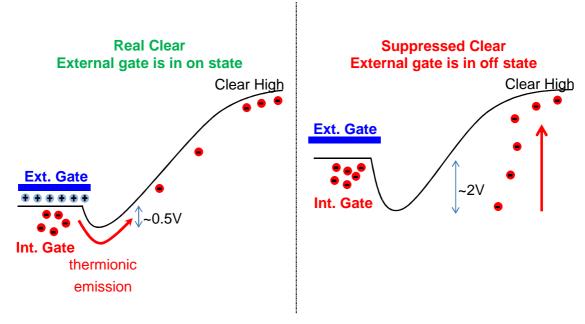

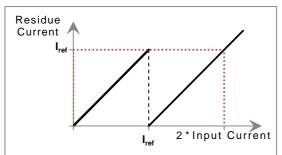

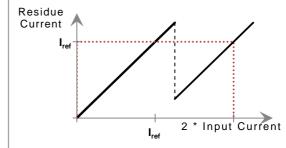

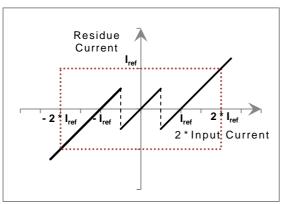

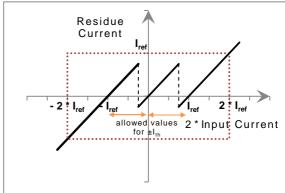

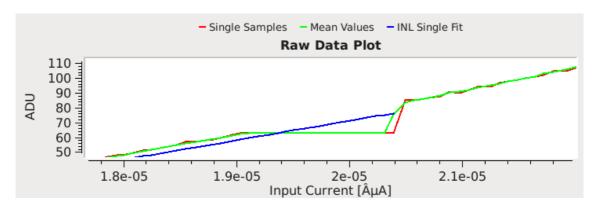

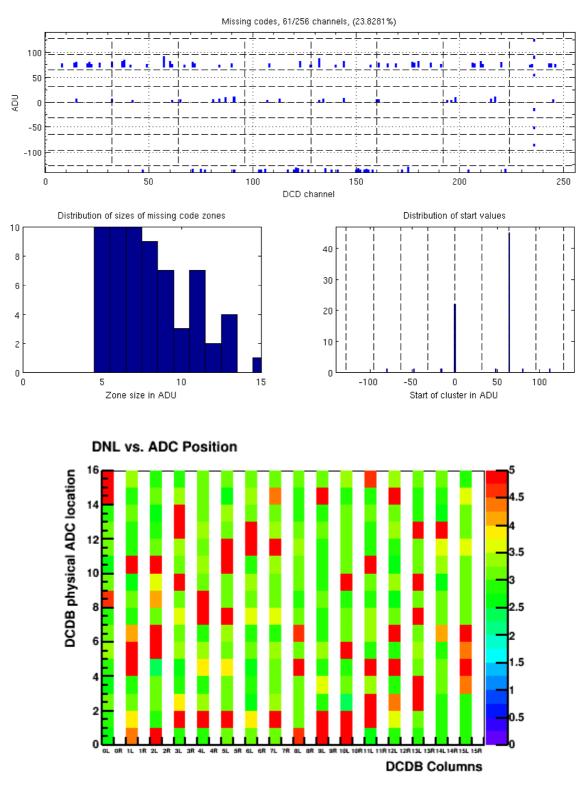

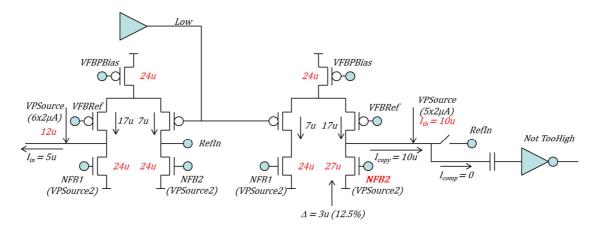

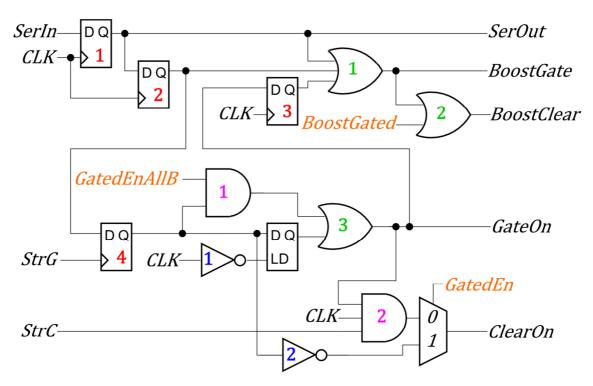

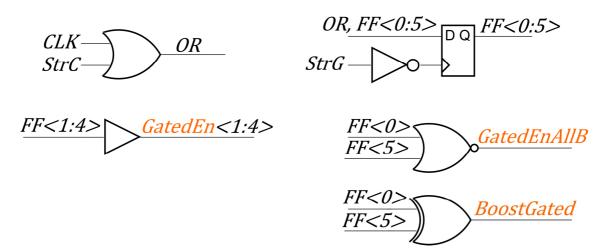

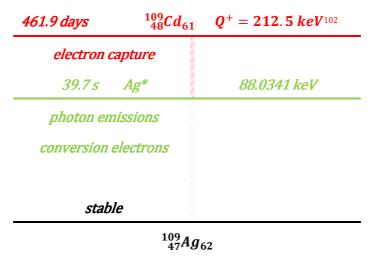

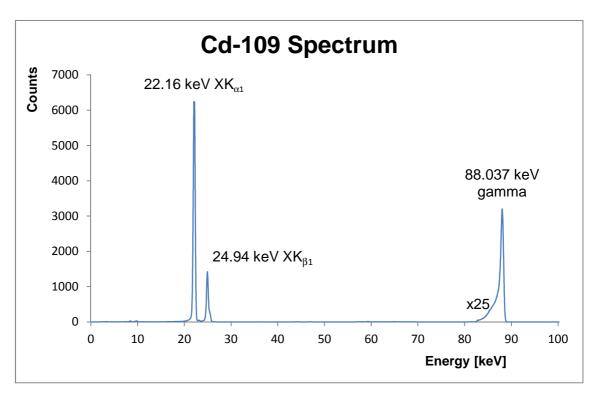

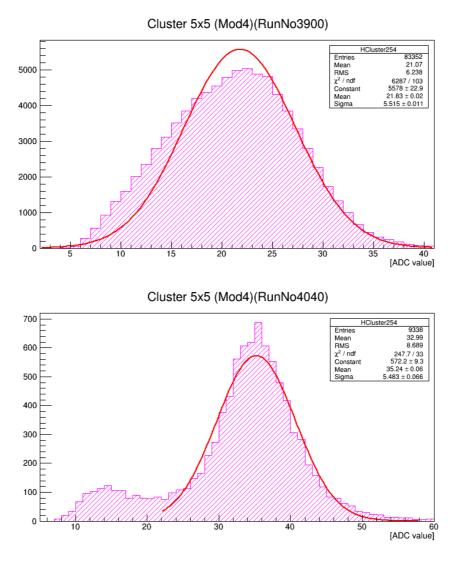

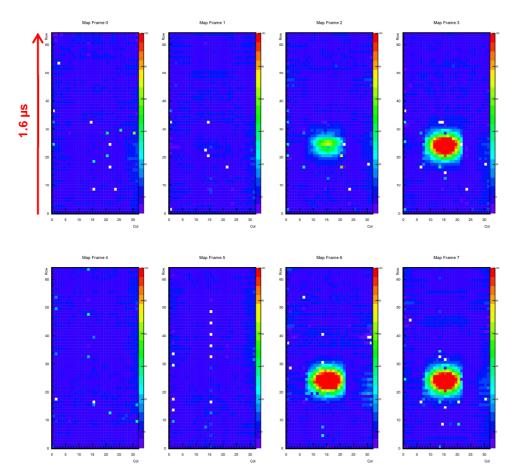

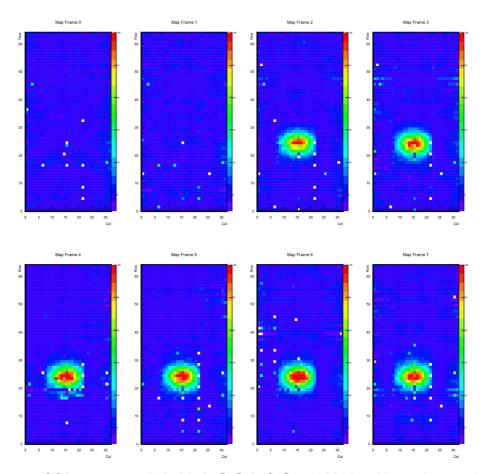

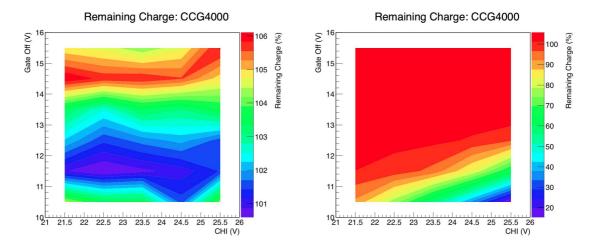

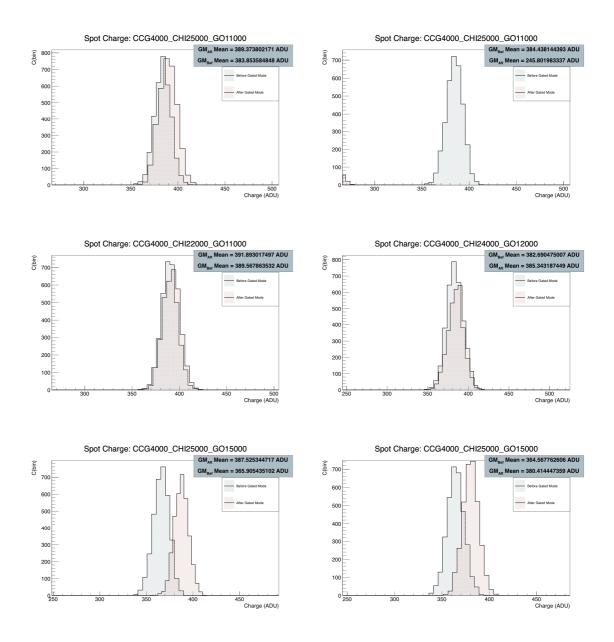

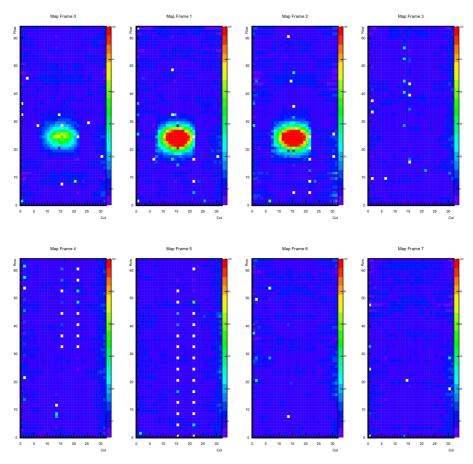

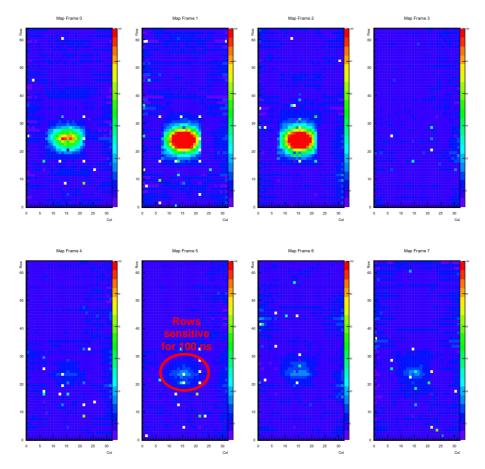

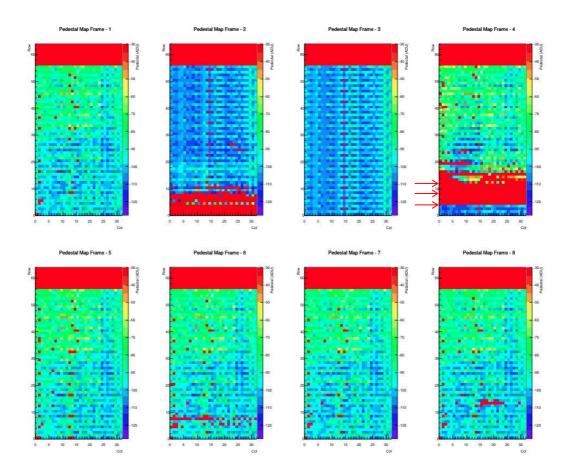

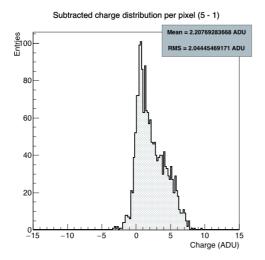

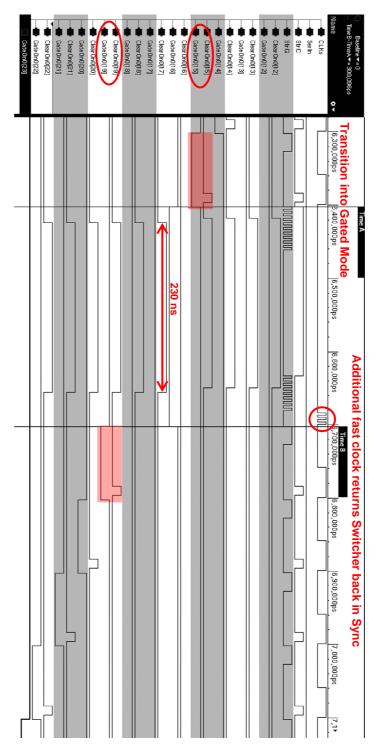

Figure 3-2: Left: cross section of DEPFET pixel with a minimum ionizing particle creating 80 electron hole pairs per µm for a 75 µm thick sensor. The electrons are attracted by the internal gate, the holes drift to the p<sup>+</sup> back contact. Right: PXD6 standard prototype design view on polysilicon and implanted layers (beige – first Poly (*Cleargate*), yellow – second Poly (*Gate*), brown – p-type implant (source, drain, drift), green – n-type implant (*Clear*). High Energy (HE) implants are used to increase the lateral drift field [43].